There are various algorithms, often mirroring what you would do to convert bases by hand, and will likely involve stateful rather than only combinatorial logic. Is that clear? I think I got all the details. One approach is to first first convert from binary to binary coded decimal. When an integer does not have a prefix, it is interpreted. You can also specify the size of the integer (the bit width) as 3, for example: B 111 does not work as you expected because 111 is in decimal format (one hundred and eleven). In the following example the loop runs through the whole set of iterations without any break to make it synthesizable. To specify an integer in binary format, you must use the b prefix.

I didnt realise that Verilog supported addition like that, (I am a complete beginner, sorry) Nevertheless, I managed to use your advice and successfully write a Ripple Carry Adder that I then converted to Binary Coded Decimal.

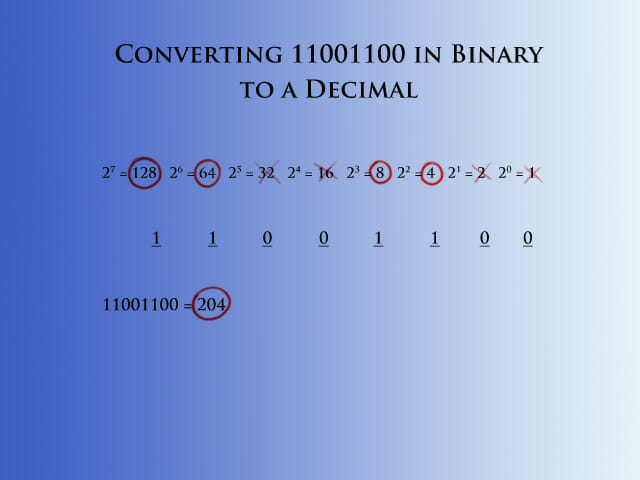

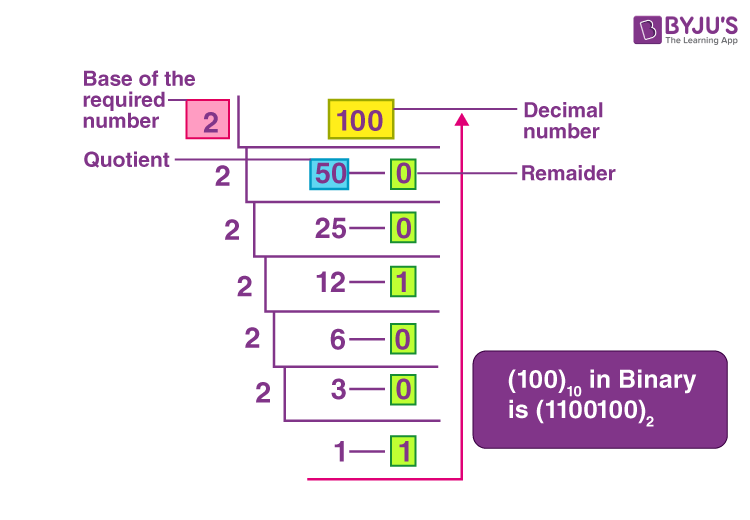

When the flag says the last digit was received the value in the accumulator can be used. Because you used logic in your example, I assumed that system verilog syntax is ok here. I mistook the + in this for boolean notation, and assumed it mean a logical OR. Of course the accumulator value is not included on the first digit (when the present value of the state machine is "IDLE". If you need to accumulate the value of the decimal number the character must be converted to a binary value and an accumulator must multiply the previous value by decimal 10 (simply add the present value to itself shifted by two and shift two more bits) and add the new binary value of the digit. GitHub - jquerius/ieee-convert: A simple routine in Verilog HDL that converts integers into IEEE 754 Floating Point format. Based on that signal the transitions are -ĭecimal = 0 then remain in IDLE and perform no action.ĭecimal = 1 then transition to NUMERIC state and perform no action.ĭecimal = 0 then transition to IDLE state and flag a number has been completed.ĭecimal = 1 then remain in NUMERIC state and perform no action. A simple routine in Verilog HDL that converts integers into IEEE 754 Floating Point format. Logic is needed to tell if the current incoming character is a decimal digit or not. If the data is arriving sequentially you will do better constructing a state machine. In parallel is simple, but uses more resources. You can detect in parallel or sequentially as you choose. If the input control 0, the circuit will count in BCD and if the input control 1, the circuit will count in gray code sequence. Divide decimal number by 2 Insert remainder into the binary number Continue since quotient (6) is. If you have any resources around this do share them. I am trying to implement a 8-bit counter that does both BCD(Binary Code decimal) and gray code sequence. To do so, use s’bn where s is an optional decimal number that indicates the size of the constant in bits b is the base format and n is the number in the specified base. Do you think just changing the width of input i.e parallel inputs instead of series would result in pattern detection? I am lost in this, please help. Except in Verilog-A, integer numbers can be explicitly expressed in decimal, hexadecimal, octal, or binary notation. > I am trying to build a sequence detector to detect a decimal number like 1092 when a stream of numbers from 0-9 is given as input. On Sunday, Novemat 12:58:16 AM UTC-4, wrote:

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed